IEEE Account

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

Thank you for visiting nature.com. You are using a browser version with limited support for CSS. To obtain the best experience, we recommend you use a more up to date browser (or turn off compatibility mode in Internet Explorer). In the meantime, to ensure continued support, we are displaying the site without styles and JavaScript.

- View all journals

- Explore content

- About the journal

- Publish with us

- Sign up for alerts

- Research Highlight

- Published: 26 July 2021

SILICON PHOTONICS

Co-packaged transceivers speed up

- Christiana Varnava 1

Nature Electronics volume 4 , page 455 ( 2021 ) Cite this article

285 Accesses

Metrics details

- Engineering

- Optical techniques

In Proc. 2021 IEEE Symposium on VLSI Technology (in the press); https://go.nature.com/3hL2gsH

Integrated optical input–output technologies are promising for high-speed communications because of their scaling and bandwidth advantages compared with electrical alternatives. Optical transceivers based on microring modulators can, for example, achieve high-throughput transmission using wavelength-division multiplexing. However, such transceivers have so far only demonstrated capacity up to 50 Gbit s –1 in the O-band (1,260 nm to 1,360 nm). Jahnavi Sharma, Hao Li and colleagues at Intel Corporation now show that a hybrid integrated transceiver based on photonic and electronic circuits can achieve a capacity up to 112 Gbit s –1 in the O-band with a pulse-amplitude modulation four-level scheme.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

24,99 € / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

111,21 € per year

only 9,27 € per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Author information

Authors and affiliations.

Nature Electronics https://www.nature.com/natelectron

Christiana Varnava

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Christiana Varnava .

Rights and permissions

Reprints and permissions

About this article

Cite this article.

Varnava, C. Co-packaged transceivers speed up. Nat Electron 4 , 455 (2021). https://doi.org/10.1038/s41928-021-00628-3

Download citation

Published : 26 July 2021

Issue Date : July 2021

DOI : https://doi.org/10.1038/s41928-021-00628-3

Share this article

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

Quick links

- Explore articles by subject

- Guide to authors

- Editorial policies

Sign up for the Nature Briefing newsletter — what matters in science, free to your inbox daily.

VLSI-SoC: Design Trends

28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6–9, 2020, Revised and Extended Selected Papers

- Conference proceedings

- © 2021

- Andrea Calimera ORCID: https://orcid.org/0000-0001-5881-3811 0 ,

- Pierre-Emmanuel Gaillardon ORCID: https://orcid.org/0000-0003-3634-3999 1 ,

- Kunal Korgaonkar ORCID: https://orcid.org/0000-0002-9078-2944 2 ,

- Shahar Kvatinsky ORCID: https://orcid.org/0000-0001-7277-7271 3 ,

- Ricardo Reis ORCID: https://orcid.org/0000-0001-5781-5858 4

Politecnico di Torino, Turin, Italy

You can also search for this editor in PubMed Google Scholar

University of Utah, Salt Lake City, USA

Technion – israel institute of technology, haifa, israel, universidade federal do rio grande do sul, porto alegre, brazil.

Part of the book series: IFIP Advances in Information and Communication Technology (IFIPAICT, volume 621)

Included in the following conference series:

- VLSI-SoC: IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip

Conference proceedings info: VLSI-SoC 2020.

19k Accesses

11 Citations

6 Altmetric

This is a preview of subscription content, log in via an institution to check access.

Access this book

- Available as EPUB and PDF

- Read on any device

- Instant download

- Own it forever

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Other ways to access

Licence this eBook for your library

Institutional subscriptions

Table of contents (16 papers)

Front matter, low-power high-speed adcs for adc-based wireline receivers in 22 nm fdsoi.

- David Cordova, Wim Cops, Yann Deval, François Rivet, Herve Lapuyade, Nicolas Nodenot et al.

Mixed-Mode Signal Processing for Implementing MCMC MIMO Detector

- Amin Aghighi, Behrouz Farhang-Boroujeny, Armin Tajalli

Low Power Current-Mode Relaxation Oscillators for Temperature and Supply Voltage Monitoring

- Shanshan Dai, Caleb R. Tulloss, Xiaoyu Lian, Kangping Hu, Sherief Reda, Jacob K. Rosenstein

Fully-Autonomous SoC Synthesis Using Customizable Cell-Based Analog and Mixed-Signal Circuits Generation

- Tutu Ajayi, Sumanth Kamineni, Morteza Fayazi, Yaswanth K. Cherivirala, Kyumin Kwon, Shourya Gupta et al.

Assessing the Configuration Space of the Open Source NVDLA Deep Learning Accelerator on a Mainstream MPSoC Platform

- Alessandro Veronesi, Davide Bertozzi, Milos Krstic

SAT-Based Mapping of Data-Flow Graphs onto Coarse-Grained Reconfigurable Arrays

- Yukio Miyasaka, Masahiro Fujita, Alan Mishchenko, John Wawrzynek

Learning Based Timing Closure on Relative Timed Design

- Tannu Sharma, Sumanth Kolluru, Kenneth S. Stevens

Multilevel Signaling for High-Speed Chiplet-to-Chiplet Communication

- Rakshith Saligram, Ankit Kaul, Muhannad S. Bakir, Arijit Raychowdhury

From Informal Specifications to an ABV Framework for Industrial Firmware Verification

- Samuele Germiniani, Moreno Bragaglio, Graziano Pravadelli

Modular Functional Testing: Targeting the Small Embedded Memories in GPUs

- Josie Esteban Rodriguez Condia, Matteo Sonza Reorda

RAT: A Lightweight Architecture Independent System-Level Soft Error Mitigation Technique

- Jonas Gava, Ricardo Reis, Luciano Ost

SANSCrypt: Sporadic-Authentication-Based Sequential Logic Encryption

- Yinghua Hu, Kaixin Yang, Shahin Nazarian, Pierluigi Nuzzo

3D Nanofabric : Layout Challenges and Solutions for Ultra-scaled Logic Designs

- Edouard Giacomin, Juergen Boemmels, Julien Ryckaert, Francky Catthoor, Pierre-Emmanuel Gaillardon

3D Logic Cells Design and Results Based on Vertical NWFET Technology Including Tied Compact Model

- Arnaud Poittevin, Chhandak Mukherjee, Ian O’Connor, Cristell Maneux, Guilhem Larrieu, Marina Deng et al.

Statistical Array Allocation and Partitioning for Compute In-Memory Fabrics

- Brian Crafton, Samuel Spetalnick, Gauthaman Murali, Tushar Krishna, Sung-Kyu Lim, Arijit Raychowdhury

abstractPIM: A Technology Backward-Compatible Compilation Flow for Processing-In-Memory

- Adi Eliahu, Rotem Ben-Hur, Ronny Ronen, Shahar Kvatinsky

Back Matter

Other volumes.

- artificial intelligence

- communication systems

- computer hardware

- computer-aided design

- distributed computer systems

- distributed systems

- embedded systems

- field programmable gate array

- integrated circuits

- microprocessor chips

- network protocols

- parallel processing systems

- signal processing

- telecommunication systems

- vlsi circuits

About this book

The 16 full papers included in this volume were carefully reviewed and selected from the 38 papers (out of 74 submissions) presented at the conference. The papers discuss the latest academic and industrial results and developments as well as future trends in the field of System-on-Chip (SoC) design, considering the challenges of nano-scale, state-of-the-art and emerging manufacturing technologies. In particular they address cutting-edge research fields like low-power design of RF, analog and mixed-signal circuits, EDA tools for the synthesis and verification of heterogenous SoCs, accelerators for cryptography and deep learning and on-chip Interconnection system, reliability and testing, and integration of 3D-ICs.

*The conference was held virtually.

Editors and Affiliations

Andrea Calimera

Pierre-Emmanuel Gaillardon

Kunal Korgaonkar, Shahar Kvatinsky

Ricardo Reis

Bibliographic Information

Book Title : VLSI-SoC: Design Trends

Book Subtitle : 28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6–9, 2020, Revised and Extended Selected Papers

Editors : Andrea Calimera, Pierre-Emmanuel Gaillardon, Kunal Korgaonkar, Shahar Kvatinsky, Ricardo Reis

Series Title : IFIP Advances in Information and Communication Technology

DOI : https://doi.org/10.1007/978-3-030-81641-4

Publisher : Springer Cham

eBook Packages : Computer Science , Computer Science (R0)

Copyright Information : IFIP International Federation for Information Processing 2021

Hardcover ISBN : 978-3-030-81640-7 Published: 15 July 2021

Softcover ISBN : 978-3-030-81643-8 Published: 15 July 2022

eBook ISBN : 978-3-030-81641-4 Published: 14 July 2021

Series ISSN : 1868-4238

Series E-ISSN : 1868-422X

Edition Number : 1

Number of Pages : XVIII, 364

Number of Illustrations : 70 b/w illustrations, 139 illustrations in colour

Topics : Computer Systems Organization and Communication Networks , Control Structures and Microprogramming , Input/Output and Data Communications , Information Systems Applications (incl. Internet)

- Publish with us

Policies and ethics

BRIDGING THE DIGITAL & PHYSICAL WORLDS with efficiency & intelligence

Add this year’s event to your calendar:

Microsoft Outlook Calendar | Google Calendar | Apple Calendar

The five-day event will include:

- Plenary Sessions, Technical Sessions

- Evening Panels

- Short Courses

- Demo Session for Outstanding Papers

- SSCS / EDS Women in Engineering & Young Professionals events

- Traditional Luau Celebration

The Symposium will feature selected presentations and panel sessions as well as advanced VLSI technology developments, innovative circuit designs, and the applications they enable, such as artificial intelligence, machine learning, IoT, wearable/implantable biomedical applications, big data, cloud / edge computing, virtual reality (VR) / augmented reality (AR), robotics, and autonomous vehicles.

Registration & Hotel Reservations Open

April 17, 2024 Full Program & Registration

SYMPOSIUM CHAIRS

Gosia Jurczak, Lam Research

Borivoje Nikolic, University of California, Berkeley

SYMPOSIUM CO-CHAIR

Takaaki Tsunomura, Tokyo Electron Ltd.

Mototsugu Hamada, The Univ. of Tokyo

PROGRAM CHAIRS

Vijay Narayanan, IBM T. J. Watson Research Center

Ron Kapusta, Analog Devices

PROGRAM CO-CHAIRS

Kazuhiko Endo, Tohoku University

Sugako Otani, Renesas Electronics

CONTACT INFO

VLSI Secretariat North America and Europe

VLSI Secretariat Japan and Far East

CONFERENCE POLICIES

Notifications & Policies

Accessibility

Non-discrimination Policy

IEEE Ethics Reporting

IEEE Privacy Policy

Call for Papers

Ca ll for Workshops

Symposium Archive

© 2024 Copyright IEEE. All rights reserved. A not-for-profit organization, IEEE is the world’s largest technical professional organization dedicated to advancing technology for the benefit of humanity.

cmos vlsi Recently Published Documents

Total documents.

- Latest Documents

- Most Cited Documents

- Contributed Authors

- Related Sources

- Related Keywords

Back propagation neural network based power estimation method for CMOS VLSI circuits

Low power vlsi design techniques: a review.

Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher side now a days even compared to dynamic power dissipation due to very high gate leakage current and subthreshold leakage. Low power consumption is equally important as speed in many applications since it leads to a reduction in the package cost and extended battery life. This paper surveys contemporary optimization techniques that aims low power dissipation in VLSI circuits.

Design of low-power CMOS VLSI circuits using multi-objective optimization in genetic algorithms

This paper presents a design CAD tool for automated design of digital CMOS VLSI circuits. In order to fit the circuit performance into desired specifications, a multi-objective optimization approach based on genetic algorithms (GA) is proposed and the transistor sizes are calculated based on the analytical equations describing the behavior of the circuit. The optimization algorithm is developed in MATLAB and the performance of the designed circuit is verified using HSPICE simulations based on 0.18µm CMOS technology parameters. Different digital integrated circuits were successfully designed and verified using the proposed design tool. It is also shown in this paper that, the design results obtained from the proposed algorithm in MATLAB, have a very good agreement with the obtained circuit simulation results in HSPICE.

Technologies for creating radiation-resistant VLSI

The technology of radiation-resistant CMOS VLSI is based on industrial IC technology. The design uses feedback circuits and guard rings to compensate for single effects of cosmic particles (SEE). In most critical cases, these influences in digital circuits lead to single faults (SEU), which temporarily disrupt the state of memory cells, to latching (SEL), and in the long term to a catastrophic change of state. Various space programs confirm great prospects for their use in future space structures. The article discusses the effects of using radiation-resistant CMOS technology, technology based on a silicon-on-sapphire structure, CMOS technology on an insulating substrate taking into account typical characteristics, SIMOX-SOI technology, which consists in separation by implantation of oxygen ions. In new designs of circuits, more advanced algorithms should be implemented for the future.

Machine Learning Based Power Estimation for CMOS VLSI Circuits

Abstract The authors have requested that this preprint be withdrawn due to a need to make corrections.

Abstract Nowdays, machine learning (ML) algorithms are receiving massive attention in most of the engineering application since it has capability in complex systems modelling using historical data. Estimation of power for CMOS VLSI circuit using various circuit attributes is proposed using passive machine learning based technique. The proposed method uses supervised learning method which provides a fast and accurate estimation of power without affecting the accuracy of the system. Power estimation using random forest algorithm is relatively new. Accurate estimation of power of CMOS VLSI circuits is estimated by using random forest model which is optimized and tuned by using multi-objective NSGA-II algorithm. It is inferred from the experimental results testing error varies from 1.4 percent to 6.8 percent and in terms of and Mean Square Error is 1.46e-06 in random forest method when compared to BPNN. Statistical estimation like coefficient of determination (𝑅) and Root Mean Square Error (RMSE) are done and it is proven that random Forest is best choice for power estimation of CMOS VLSI circuits with high coefficient of determination of 0.99938. and low RMSE of 0.000116.

Leakage Power Reduction in CMOS VLSI Circuits using Advance Leakage Reduction Method

Recently, consumption of power is key problem of logic circuits based on Very Large Scale Integration. More potentiality consumption isn’t considered an appropriate for storage cell life for the use in cell operations and changes parameters such as optimality, efficiency etc, more consumption of power also provides for minimization of cell storage cycle. In present scenario static consumption of power is major troubles in logic circuits based on CMOS. Layout of drainage less circuit is typically complex. Several derived methods for minimization of consumption of potentiality for logic circuits based on CMOS. For this research paper, a technique called Advance Leakage reduction (AL reduction) is proposed to reduce the leakage power in CMOS logic circuits. To draw our structure circuit related to CMOS like Inverter, inverted AND, and NOR etc. we have seen the power and delay for circuits. This paper incorporates, analyzing of several minimization techniques as compared with proposed work to illustrate minimization in ratio of energy and time usage and time duration for propagation. LECTOR, Source biasing, Stack ONOFIC method is observed and analyzed with the proposed method to evaluate the leakage power consumption and propagation delay for logic circuits based on CMOS. Entire work has done in LT Spice Software with 180nm library of CMOS.

Revisiting the Utility of Transmission Gate and Passtransistor Logic Styles in CMOS VLSI Design

Peculiarities of appearance and registration of the latchup in cmos vlsi under uniform pulsed laser irradiation, export citation format, share document.

International Journal For Multidisciplinary Research

A widely indexed open access peer reviewed multidisciplinary bi-monthly scholarly international journal.

Volume 6 Issue 3 May-June 2024

Submit your research paper

Review on Power Reduction Technology in VLSI Multiplier

CrossRef DOI is assigned to each research paper published in our journal.

IJFMR DOI prefix is 10.36948/ijfmr

All research papers published on this website are licensed under Creative Commons Attribution-ShareAlike 4.0 International License , and all rights belong to their respective authors/researchers.

VLSI 2020: IBM Research highlights nanosheet, AI processor and photonics advances

At the 2020 Symposia on VLSI Technology and Circuits this week, IBM Research is presenting a variety of papers, short courses, workshops and virtual sessions that demonstrate the latest advances in systems research. Our research spotlights key developments for hybrid cloud infrastructure and AI , marked by improvements in performance, energy efficiency, area scaling, and new workloads.

At VLSI’s first-ever virtual conference, IBM researchers are presenting their work on a universal air spacer compatible with different transistor architectures, whether it’s a fin field-effect transistor (FinFET) or a Nanosheet device architecture. Another team of IBM researchers demonstrates a new AI processor core design resulting in hardware utilization improvements that led to notable enhancements in training efficiency and performance. In a third paper, researchers focused on faster silicon photonics-based network switching, with one goal of eventually making these networks more useful for data centers.

The new air spacer design, taken by a transmission electron microscope.

In their paper, “Improved Air Spacer Co-Integrated with Self-Aligned Contact (SAC) and Contact Over Active Gate (COAG) for Highly Scaled CMOS Technology,” IBM researchers described how the new air spacer reduces effective capacitance – a critical factor impacting the characteristics of CMOS devices – by 15 percent through a reduction in the air spacer’s dielectric constant, leading to performance gains and power reductions at the same time. Although SAC and COAG have been adopted in FinFET technology to reduce the footprint of transistors and standard cells, co-integrating air spacers with SAC and COAG has been challenging.

The spacer is an isolation layer between a gate and the contacts for source and drain in the transistor – essentially, an electronic switch. When the gate is on, electricity flows from the source to the drain, and the gate serves as a valve. The spacer ensures the gate controls only the flow and that the gate and the source and drain are electrically isolated. Without the spacer, the gate cannot serve as a valve.

Researchers positioned their improved air spacer as a viable approach to enhance energy efficiency and performance of advanced CMOS technology by reducing parasitic capacitance, the unwanted capacitance between the parts of an electronic component or circuit due to their proximity to one another.

The paper introduces a new process to form air spacers and provides a practical approach to enabling an electronic device to consume less power while achieving better performance. Excitingly, introducing the new air spacer module into 7nm FinFET produces more performance gains than more costly and disruptive scaling of FinFET to 5nm. The researchers expect their work will help pave the way for their technology’s adoption in FinFET and NanoSheet transistors in the coming years.

Paper authors: Kangguo Cheng, Chanro Park, Heng Wu, Juntao Li, Son Nguyen, Jingyun Zhang, Miaomiao Wang, Sanjay Mehta, Zuoguang Liu, Richard Conti, Nicolas Loubet, Julien Frougier, Andrew Greene, Tenko Yamashita, Bala Haran, Rama Divakaruni

AI Processor Core

The Digital AI Core with heterogeneous compute engines, featuring dual corelet architecture, shared L1 scratchpad, and memory neighbor interface.

A worldwide team of IBM researchers described a hardware demonstration of a processor core that can be applied to both AI training and inference applications in their paper, “A 3.0 TFLOPS 0.62V Scalable Processor Core for High Compute Utilization AI Training and Inference.” The researchers achieved leading-edge compute efficiency for robust AI computations via efficient heterogeneous 2-D systolic array-SIMD (single instruction, multiple data) compute engines leveraging compact DLFloat16 Floating Point Units (FPUs). DLFloat is a 16-bit floating point format designed by IBM for deep learning training and inference.

For this study, the researchers optimized a Gen 1 core they first published in 2018, focusing on circuit design, architecture, and software enhancements to produce testchips with Gen 2 cores. This updated Gen 2 design features two corelets working in parallel and sharing memory to facilitate efficient computations. The resulting Gen 2 testchip achieved 5.5x power-efficiency improvements over their Gen 1 testchip for Deep Learning training and inference workflows while using a smaller supply voltage than their first-generation core. Each of the two corelets in the new design has 64 processing elements (each with multiple FPUs) that perform convolution and matrix multiplication operations, which is greater than 80 percent of overall workload in deep learning.

This advancement is part of the Digital AI Core accelerator research in the IBM Research AI Hardware Center . AI hardware accelerators can be used for building and deploying neural network models for applications such as speech recognition, natural language processing and computer vision. This latest chip focuses on 16-bit training and inference, but the researchers have also published progress towards 8 bit training and inference as low as 2 bits .

Paper authors: Jinwook Oh, SaeKyu Lee, Mingu Kang, Matthew Ziegler, Joel Silberman, Ankur Agrawal, Swagath Venkataramani, Bruce Fleischer, Michael Guillorn, Jungwook Choi, WeiWang, Silvia Mueller, Shimon Ben-Yehuda, James Bonanno, Nianzheng Cao, Robert Casatuta, Chia-Yu Chen, Matt Cohen, Ophir Erez, Thomas Fox, George Gristede, Howard Haynie, Vicktoria Ivanov, Siyu Koswatta, Shih-Hsien Lo, Martin Lutz, Gary Maier, Alex Mesh, Yevgeny Nustov, Scot Rider, Marcel Schaal, Michael Scheuermann, Xiao Sun, Naigang Wang, Fanchieh Yee, Ching Zhou, Vinay Shah, Brian Curran, Vijayalakshmi Srinivasan, Pong-Fei Lu, Sunil Shukla, Kailash Gopalakrishnan, Leland Chang

Silicon Photonics

The silicon photonics switch module.

In the paper, “A Monolithically Integrated Silicon Photonics 8×8 Switch in 90nm SOI CMOS,” IBM researchers from the U.S. and Canada presented a silicon photonics-based network switch integrated with switching and control electronics. Silicon photonics, an evolving technology in which optical rays transfer data between computer chips, provides an affordable way to build faster switches. Optical rays can carry far more data in less time than electrical conductors.

IBM researchers have created one of the best performing high speed photonic switches, closing the performance gap with packet switching, which the internet uses to send data as well as information about where the data should be delivered. They have also simplified many problems that arise when trying to build electronics and photonics on the same chip. Their goal is to include all of the necessary electronics in order to reduce the packaging load and make a switch that’s both easier to manufacture and more affordable to implement.

The new optical-based circuit switching technology enables switch reconfiguration times of less than 15 nanoseconds while avoiding the high power of more conventional packet-based electronic switches, which require optical-to-electronic domain conversion. The technology uses a scalable process with simple flip chip packaging. Flip chip is a method for interconnecting integrated circuit chips, microelectromechanical systems, or other semiconductor components to external circuitry.

Paper authors: Jonathan E. Proesel, Nicolas Dupuis, Herschel Ainspan, Christian W. Baks, Fuad Doany, Nicolas Boyer, Elaine Cyr, Benjamin G. Lee

Additional Works

Other accepted VLSI papers from IBM and AI Hardware Center members, in addition to those above, include:

“Selective Enablement of Dual Dipoles for Near Bandedge Multi-Vt Solution in High Performance FinFET and Nanosheet Technologies,” R. Bao, K. Watanabe, J. Zhang, H. Zhou, M. Sankarapandian, J. Li, S. Pancharatnam, P. Jamison, R. G Southwick, M. Wang, J. J Demarest, J. Guo, N. Loubet, V. Basker, D. Guo, V. Narayanan, B. Haran, H. Bu, M. Khare

“Si Incorporation Into AsSeGe Chalcogenides for High Thermal Stability, High Endurance and Extremely Low Vth Drift 3D Stackable Cross-point Memory,” H. Y. Cheng, I. T. Kuo, W C. Chien, C. W. Yeh, Y. C. Chou, N. Gong, L. Gignac, C. H. Yang, C. W. Cheng, C. Lavoie, M. Hopstaken, B. R. Bruce, L. Buzi, E. K. Lai, F. Carta, A. Ray, M. H. Lee, H. Y.Ho, W. Kim, M. BrightSky, H. L. Lung

“Structural and Electrical Demonstration of SiGe Cladded Channel for PMOS Stacked Nanosheet Gate-All-Around Devices,” S.Mochizuki, B.Colombeau, J.Zhang, S. C.Kung, M.Stolfi, H. Zhou, M. Breton, K. Watanabe, J. Li, H. Jagannathan, M.Cogorno, T.Mandrekar, P.Chen, N. Loubet, S.Natarajan, B.Haran

“Composite Interconnects for High-Performance Computing Beyond the 7nm Node” P. Bhosale, S. Parikh, N. Lanzillo, T. Nogami, R. Tao, M. Gage, R. Shaviv, A. Simon, M. Stolfi, S. Reidy, N.Loubet, B. Haran

“A no-verification Multi-Level-Cell (MLC) operation in Cross-Point OTS-PCM” N. Gong, W. Chien, Y. Chou, C. Yeh, N. Li, H. Cheng, C. Cheng, I. Kuo, C. Yang, R. Bruce, A. Ray, L. Gignac, Y. Lin, C. Miller, T. Perri, W. Kim, L. Buzi, H. Utomo, F. Carta, E. Lai, H. Ho, H. Lung, M. BrightSky

“A 25-50Gb/s 2.22pJ/b NRZ RX with Dual-Bank and 3-tap Speculative DFE for Microprocessor Application in 7nm FinFET CMOS” Y. You, G. Wiedemeier, C. Marquart, C. Steffen, E. English, De. Yilma, T. Pham, V. Nammi, J. Okyere, N. Blanchard, A. Sutton, Z. Zhang, D. Friend D. Barba, T. Bohlke, M. Spear, V. Raj, J. Crugnale, D. Dreps, P.A. Francese, M. Kossel, T. Morf

Additionally, at VLSI:

- Alberto Valdes-Garcia will give an invited talk on “Hardware-Software Co-Integration for Configurable 5G mmWave Systems” (Circuits JFS2.1 session)

- Mukta Farooq and Arvind Kumar will offer a short course on “ Heterogenous Integration Architectures for AI ”

- Nicholas Loubet will offer a short course on “ Nanosheet Transistor as a Replacement of FinFET for Future Nodes: Device Advantages & Specific Process Elements ”

- Mounir Meghelli will offer a short course on “ Advances and Trends in High-Speed Serial Links for High-Density IO Applications ”

- Robert Bruce will offer a workshop presentation on “ Designing Material Systems and Algorithms for Analog Computing ”

These advances are part of IBM’s systems research group, which includes initiatives focusing on hybrid cloud, AI hardware, and exploratory science.

- Kangguo Cheng

Purdue Hospitality and Tourism Management graduate student wins best paper award for innovative technology research

Written By: Rebecca Hoffa, [email protected]

Evita Ma poses with the fellow Purdue HTM attendees at the 29th Annual Graduate Education and Graduate Student Research Conference in Hospitality and Tourism in January. (Photo provided)

As Starship robots deliver food to hungry Boilermakers across Purdue University’s West Lafayette campus, their presence is often welcomed like that of a neighborhood pet — students are often seen helping them when they get stuck or smiling and moving out of their way when they meet them on the sidewalk. When Alei (Aileen) Fan , associate professor in the White Lodging-J.W. Marriott, Jr. School of Hospitality and Tourism Management (HTM) and an expert in service innovation and experience design, helped one along its way one day, she was met with a low-tone, male voice saying, “Thank you.” This contradicted the “cute” vision Fan had in her mind of the robots being like her dog at home.

When Fan relayed the experience to her PhD student Chang (Evita) Ma , the College of Health and Human Sciences graduate student was inspired to investigate deeper how the combination of appearance and voice impacted the consumer’s overall experience in the service encounter.

Evita Ma poses with her best paper award at the 29th Annual Graduate Education and Graduate Student Research Conference in Hospitality and Tourism. (Photo provided)

These efforts culminated in winning a best paper award at the 29th Annual Graduate Education and Graduate Student Research Conference in Hospitality and Tourism in January.

“I’m really honored,” Ma said. “As far as I know, for the past three years or so, no one from our school has gotten the award, so it was a pleasure to have that. It’s very competitive — over the 130-some presentations, I was selected as one of the four winners.”

The study looked at how people’s reactions differed when comparing matched, or congruent, voice and appearance and mismatched, or incongruent, voice and appearance. The researchers found that depending on the robot’s function, people tended to be either more or less accepting of when a robot’s voice does not match its appearance.

In a utilitarian scenario where the consumer really only desires the robot to perform a job function and doesn’t care as much about having an emotional connection, people often prefer the congruent voice and appearance because they feel the incongruent one is not well-designed or not capable of performing their desired outcome. When consumers are in a hedonic scenario where they don’t care as much about the functions the robot is performing but simply wish to have a connection or engage with the robot, the congruency doesn’t matter as much, and some of the surprising elements, such as the mismatched voice and appearance, may attract people to engage with it.

“We as human beings actually view things holistically,” Ma said. “We don’t separate the different parts.”

Considering how these distinct factors work together to shape consumer perceptions could ultimately shape the characteristics of future service robots to improve service encounters across the industry.

“It’s a timely topic,” Fan said. “Whether you like it or not, technology takes up a lot of our lives. This research provided practical guidelines for industries and companies on how to design different robots to better serve our customer.”

This study resulted as a product of Ma’s study “Decoding the Shared Pathways of Consumer Technology Experience in Hospitality and Tourism: A Meta-Analysis,” which examined the literature currently available to investigate the different types of technology and how humans interact with them. Ma ultimately noticed a gap in papers that combined elements — many simply looked at appearance or voice independently.

“Very few of the papers actually combine all the different subtle elements together; they just focus on one single perspective like appearance or voice,” Ma said. “So, I began looking at: What is the combination between those? Our initial idea was we wanted to know how the combination of design elements of service robots impacts the customer’s reactions and feelings of the service in different scenarios.”

Prior to coming to Purdue, Ma spent four years gaining industry experience at the Hospitality Financial and Technology Professionals nonprofit in Hong Kong, where she made many connections on the technology side of the industry and solidified her interest in coming to a very technology-focused university to earn her PhD.

“Purdue has such a strong background in terms of technology and engineering, so that was also one of the reasons I wanted to keep focusing on that for my research area,” Ma said. “After taking a class with Dr. Fan, I decided to join her team.”

Beyond research, Ma has fully immersed herself in the teaching and engagement areas of graduate student life as well. Ma teaches two 200-level marketing courses to undergraduate HTM students, where she’s maximized opportunities for the students to engage in experiential education. She’s also working on curriculum development with HTM faculty and has become involved in several graduate student organizations, including the Purdue Graduate Student Government, where she is a senator.

After graduating from the program, Ma plans to pursue a faculty position that allows her to combine her passion for research with her love for teaching and service.

“She’s really the star student,” Fan said. “When we evaluate a PhD student, there are three aspects: research, teaching and service. Evita is excellent in all of these.”

Suggestions or feedback?

MIT News | Massachusetts Institute of Technology

- Machine learning

- Social justice

- Black holes

- Classes and programs

Departments

- Aeronautics and Astronautics

- Brain and Cognitive Sciences

- Architecture

- Political Science

- Mechanical Engineering

Centers, Labs, & Programs

- Abdul Latif Jameel Poverty Action Lab (J-PAL)

- Picower Institute for Learning and Memory

- Lincoln Laboratory

- School of Architecture + Planning

- School of Engineering

- School of Humanities, Arts, and Social Sciences

- Sloan School of Management

- School of Science

- MIT Schwarzman College of Computing

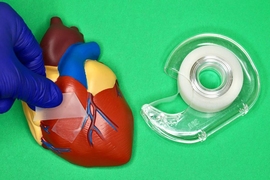

Adhesive coatings can prevent scarring around medical implants

Press contact :, media download.

*Terms of Use:

Images for download on the MIT News office website are made available to non-commercial entities, press and the general public under a Creative Commons Attribution Non-Commercial No Derivatives license . You may not alter the images provided, other than to crop them to size. A credit line must be used when reproducing images; if one is not provided below, credit the images to "MIT."

Previous image Next image

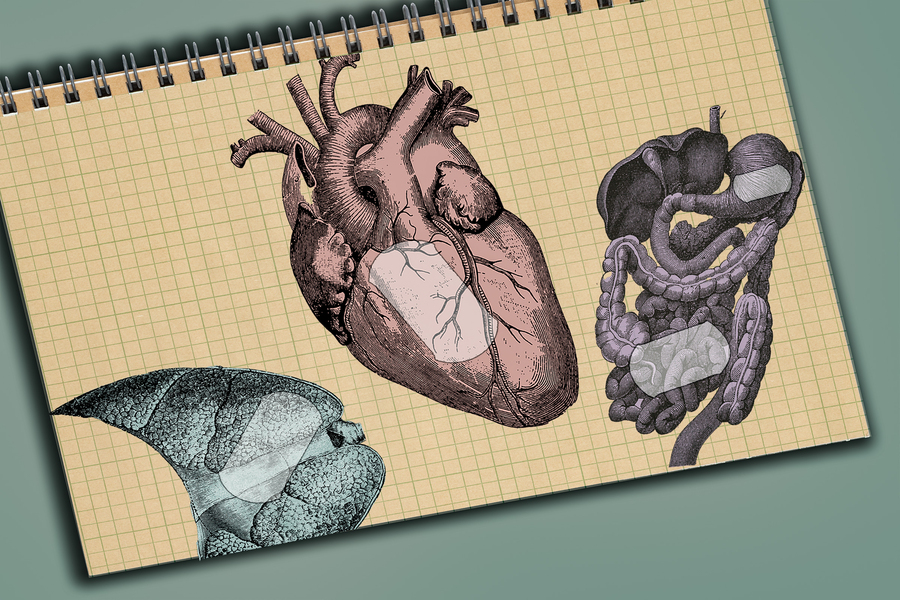

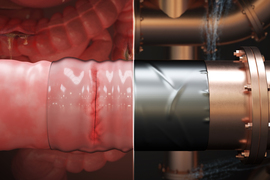

When medical devices such as pacemakers are implanted in the body, they usually provoke an immune response that leads to buildup of scar tissue around the implant. This scarring, known as fibrosis, can interfere with the devices’ function and may require them to be removed.

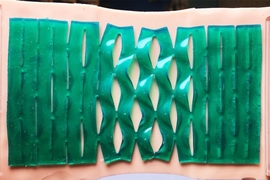

In an advance that could prevent that kind of device failure, MIT engineers have found a simple and general way to eliminate fibrosis by coating devices with a hydrogel adhesive. This adhesive binds the devices to tissue and prevents the immune system from attacking it.

“The dream of many research groups and companies is to implant something into the body that over the long term the body will not see, and the device can provide therapeutic or diagnostic functionality. Now we have such an ‘invisibility cloak,’ and this is very general: There’s no need for a drug, no need for a special polymer,” says Xuanhe Zhao, an MIT professor of mechanical engineering and of civil and environmental engineering.

The adhesive that the researchers used in this study is made from cross-linked polymers called hydrogels, and is similar to a surgical tape they previously developed to help seal internal wounds. Other types of hydrogel adhesives can also protect against fibrosis, the researchers found, and they believe this approach could be used for not only pacemakers but also sensors or devices that deliver drugs or therapeutic cells.

Zhao and Hyunwoo Yuk SM ’16, PhD ’21, a former MIT research scientist who is now the chief technology officer at SanaHeal, are the senior authors of the study, which appears today in Nature . MIT postdoc Jingjing Wu is the lead author of the paper.

Preventing fibrosis

In recent years, Zhao’s lab has developed adhesives for a variety of medical applications, including double-sided and single-sided tapes that could be used to heal surgical incisions or internal injuries. These adhesives work by rapidly absorbing water from wet tissues, using polyacrylic acid, an absorbent material used in diapers. Once the water is cleared, chemical groups called NHS esters embedded in the polyacrylic acid form strong bonds with proteins at the tissue surface. This process takes about five seconds.

Several years ago, Zhao and Yuk began exploring whether this kind of adhesive could also help keep medical implants in place and prevent fibrosis from occurring.

To test this idea, Wu coated polyurethane devices with their adhesive and implanted them on the abdominal wall, colon, stomach, lung, or heart of rats. Weeks later, they removed the device and found that there was no visible scar tissue. Additional tests with other animal models showed the same thing: Wherever the adhesive-coated devices were implanted, fibrosis did not occur, for up to three months.

“This work really has identified a very general strategy, not only for one animal model, one organ, or one application,” Wu says. “Across all of these animal models, we have consistent, reproducible results without any observable fibrotic capsule.”

Using bulk RNA sequencing and fluorescent imaging, the researchers analyzed the animals’ immune response and found that when devices with adhesive coatings were first implanted, immune cells such as neutrophils began to infiltrate the area. However, the attacks quickly quenched out before any scar tissue could form.

“For the adhered devices, there is an acute inflammatory response because it is a foreign material,” Yuk says. “However, very quickly that inflammatory response decayed, and then from that point you do not have this fibrosis formation.”

One application for this adhesive could be coatings for epicardial pacemakers — devices that are placed on the heart to help control the heart rate. The wires that contact the heart often become fibrotic, but the MIT team found that when they implanted adhesive-coated wires in rats, they remained functional for at least three months, with no scar tissue formation.

“The formation of fibrotic tissue at the interface between implanted medical devices and the target tissue is a longstanding problem that routinely causes failure of the device. The demonstration that robust adhesion between the device and the tissue obviates fibrotic tissue formation is an important observation that has many potential applications in the medical device space,” says David Mooney, a professor of bioengineering at Harvard University, who was not involved in the study.

Mechanical cues

The researchers also tested a hydrogel adhesive that includes chitosan, a naturally occurring polysaccharide, and found that this adhesive also eliminated fibrosis in animal studies. However, two commercially available tissue adhesives that they tested did not show this antifibrotic effect because the commercially available adhesives eventually detached from the tissue and allowed the immune system to attack.

In another experiment, the researchers coated implants in hydrogel adhesives but then soaked them in a solution that removed the polymers’ adhesive properties, while keeping their overall chemical structure the same. After being implanted in the body, where they were held in place by sutures, fibrotic scarring occurred. This suggests that there is something about the mechanical interaction between the adhesive and the tissue that prevents the immune system from attacking, the researchers say.

“Previous research in immunology has been focused on chemistry and biochemistry, but mechanics and physics may play equivalent roles, and we should pay attention to those mechanical and physical cues in immunological responses,” says Zhao, who now plans to further investigate how those mechanical cues affect the immune system.

Yuk, Zhao, and others have started a company called SanaHeal, which is now working on further developing tissue adhesives for medical applications.

“As a team, we are interested in reporting this to the community and sparking speculation and imagination as to where this can go,” Yuk says. “There are so many scenarios in which people want to interface with foreign or manmade material in the body, like implantable devices, drug depots, or cell depots.”

The research was funded by the National Institutes of Health and the National Science Foundation.

Share this news article on:

Press mentions, interesting engineering.

MIT engineers have developed a new adhesive, low-cost hydrogel that can stop fibrosis often experienced by people with pacemakers and other medical devices, reports for Maria Bolevich Interesting Engineering . “These findings may offer a promising strategy for long-term anti-fibrotic implant–tissue interfaces,” explains Prof. Xuanhe Zhao.

Previous item Next item

Related Links

- Xuanhe Zhao

- Hyunwoo Yuk

- Jingjing Wu

- Department of Mechanical Engineering

- Department of Civil and Environmental Engineering

Related Topics

- Mechanical engineering

- Civil and environmental engineering

- Biomedical engineering

- Medical devices

- National Institutes of Health (NIH)

- National Science Foundation (NSF)

Related Articles

Engineers develop surgical “duct tape” as an alternative to sutures

Double-sided tape for tissues could replace surgical sutures

Super-strong surgical tape detaches on demand

Paper-folding art inspires better bandages

More mit news.

Scientists identify mechanism behind drug resistance in malaria parasite

Read full story →

Getting to systemic sustainability

New MIT-LUMA Lab created to address climate challenges in the Mediterranean region

MIT Press releases Direct to Open impact report

Modeling the threat of nuclear war

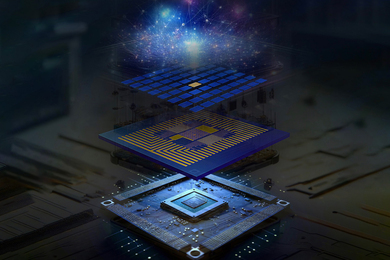

Modular, scalable hardware architecture for a quantum computer

- More news on MIT News homepage →

Massachusetts Institute of Technology 77 Massachusetts Avenue, Cambridge, MA, USA

- Map (opens in new window)

- Events (opens in new window)

- People (opens in new window)

- Careers (opens in new window)

- Accessibility

- Social Media Hub

- MIT on Facebook

- MIT on YouTube

- MIT on Instagram

IMAGES

VIDEO

COMMENTS

Read all the papers in 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) | IEEE Conference | IEEE Xplore

Explore the latest full-text research PDFs, articles, conference papers, preprints and more on VLSI TECHNOLOGY. Find methods information, sources, references or conduct a literature review on VLSI ...

Different areas of VLSI Technology reviewed in the paper. This work thoroughly attempts to summarize the literature on AI/ML algorithms for VLSI design and modeling at different abstraction levels. It is the first paper that provides a detailed review encompassing circuit modeling to system-on-chip (SoC) design, along with physical design ...

The development of complementary metal-oxide-semiconductor (CMOS) technology brought about a new paradigm for low-power circuit design. For the implementation of digital circuits with very large-scale integration, CMOS design styles are frequently employed in VLSI. There are billions of transistors on a single die in today's IC devices.

different levels of VLSI design. His paper included a brief on the existing VLSI-AI tools and stressed the importance of incorporating the expanded capabilities of AI in CAD tools. The advantages of incorporating AI in the VLSI design pro- cess and its applications are briefed in [16] and [17]. Khan et

Co-packaged transceivers speed up. Integrated optical input-output technologies are promising for high-speed communications because of their scaling and bandwidth advantages compared with ...

The VLSI industry has grown a lot for several decades. The Packing density of integrated circuits has been increased without compromising the functionality. Scaling of semiconductor devices, improvements in process technology and the development of new device designs are the key to this. Starting from the planar MOSFETs to novel multigate transistors, semiconductor devices have a history of ...

The VLSI-SoC 2020 proceedings present cutting-edge research on very large scale integration, low-power design of RF, and more. VLSI-SoC: Design Trends: 28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6-9, 2020, Revised and Extended Selected Papers | SpringerLink

PDF | On Sep 2, 2023, Rimi Das and others published AI in VLSI Design Advances and Challenges: Living in the Complex Nature of Integrated Devices | Find, read and cite all the research you need on ...

The 2024 IEEE Symposium on VLSI Technology & Circuits will be held as an in-person event with on demand content. Welcome to the 2024 IEEE Symposium on VLSI Technology & Circuits. We appreciate your interest in submitting a paper to the Symposium. On this page, you will find all the necessary information and forms for the preparation of your ...

Feature papers represent the most advanced research with significant potential for high impact in the field. ... VLSI signal processing; digital systems; system on ... technology for decoders with code length 128. We show that the new decoders outperform state-of-the-art reference decoders. For list size 8, improvements of up to 158.8 % and 62. ...

The 2022 IEEE Symposium on VLSI Technology and Circuits will run from June 13-17th in Honolulu, HI, and offer limited access to conference content on-demand. Researchers present 13 papers, including results of a new advanced CMOS FinFET technology, Intel 4, demonstrating more than 20% performance gain at iso-power over Intel 7.

The five-day event will include: The Symposium will feature selected presentations and panel sessions as well as advanced VLSI technology developments, innovative circuit designs, and the applications they enable, such as artificial intelligence, machine learning, IoT, wearable/implantable biomedical applications, big data, cloud / edge ...

Cmos Vlsi. Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher ...

Employing AI and machine learning (ML) algorithms. in VLSI design and manufacturing reduces the time and effort. for understanding and processing the data within and across. different abstraction ...

Review on Power Reduction Technology in VLSI Multiplier - Priti G Ingle, Amol S Baile, Shubhangi Joshi - IJFMR Volume 5, Issue 6, November-December 2023. DOI 10.36948/ijfmr.2023.v05i06.10532 ... View / Download PDF File. Share this. E-ISSN 2582-2160. doi. CrossRef DOI is assigned to each research paper published in our journal. IJFMR DOI prefix ...

At the 2020 Symposia on VLSI Technology and Circuits this week, IBM Research is presenting a variety of papers, short courses, workshops and virtual sessions that demonstrate the latest advances in systems research. Our research spotlights key developments for hybrid cloud infrastructure and AI, marked by improvements in performance, energy efficiency, area scaling, and new workloads.

@article{Zhang2024ResearchSA, title={Research Status and Prospects of Ultrasonic Vibration-Assisted Joining Technology for Difficult-to-Weld High-Strength Alloys}, author={Yue Zhang and Jianbiao Peng and Ruitao Peng and Jiachuan Jiang and Bei Lei and Changhui Liao and ChangYou Xu}, journal={Metals and Materials International}, year={2024}, url ...

We are proposing a brand new architecture and a fabrication technology that can support the scalability requirements of a hardware system for a quantum computer," says Linsen Li, an electrical engineering and computer science (EECS) graduate student and lead author of a paper on this architecture.

Data integration is considered a classic research field and a pressing need within the information science community. Ontologies play a critical role in such processes by providing well-consolidated support to link and semantically integrate datasets via interoperability. This paper approaches data integration from an application perspective by looking at ontology matching techniques.

Herrera-Arcos is the lead author of the paper. Optogenetic control. For decades, researchers have been exploring the use of functional electrical stimulation (FES) to control muscles in the body. This method involves implanting electrodes that stimulate nerve fibers, causing a muscle to contract.

VLSI DESIGN AND FUTURE OF DIGITAL. SYSTEMS. N.Govardhan, Dr.Ravichander Janapati, Mahender kommabatla. ABSTRACT. Very-large-scale in tegration (V LSI) is the operation of cultivating an Integrated ...

In a paper titled "tRNA modification reprogramming contributes to artemisinin resistance in Plasmodium falciparum", published in the journal Nature Microbiology, researchers from SMART's Antimicrobial Resistance (AMR) interdisciplinary research group documented their discovery: A change in a single tRNA, a small RNA molecule that is involved in translating genetic information from RNA to ...

Purdue Hospitality and Tourism Management graduate student wins best paper award for innovative technology research; Purdue HTM students take inaugural trip to Washington, D.C., through exclusive leadership program; Purdue researchers introduce novel machine-learning technique to detect age-related changes in tremors

Zhao and Hyunwoo Yuk SM '16, PhD '21, a former MIT research scientist who is now the chief technology officer at SanaHeal, are the senior authors of the study, which appears today in Nature. MIT postdoc Jingjing Wu is the lead author of the paper. Preventing fibrosis