The IEEE Circuits and Systems Society is the leading organization that promotes the advancement of the theory, analysis, computer-aided design and practical implementation of circuits, and the application of circuit theoretic techniques to systems and signal processing. The Society brings engineers, researchers, scientists and others involved in circuits and systems applications access to the industry’s most essential technical information, networking opportunities, career development tools, and many other exclusive benefits.

More Information

Visit CASS MiLe

The IEEE International Symposium on Circuits and Systems (ISCAS) is the flagship conference of the IEEE Circuits and Systems (CAS) Society and the world’s premiere forum for researchers in the active fields of theory, design and implementation of circuits and systems. This is accomplished through technical conference sessions, poster sessions, live demonstration sessions, and publication of conference papers. ISCAS 2024 is inspired by the theme "circuits and systems for sustainable development", which is perfectly aligned with the host city's goal.

2024 IEEE 22nd Interregional NEWCAS Conference

2024 ieee international conference on multimedia and expo, 2024 ieee/acm international symposium on low power electronics and design.

IEEE Transactions on Very Large Scale Integration Systems

Publication menu.

IEEE Transactions on Very Large Scale Integration (VLSI) Systems covers design and realization of microelectronic systems using VLSI/ULSI technologies that require close collaboration among scientists and engineers in the fields of systems architecture, logic and circuit design, chips and wafer fabrication, packaging, testing and systems applications. Generation of specifications, design and verification must be performed at all abstraction levels, including the system, register-transfer, logic, circuit, transistor and process levels.

To address this critical area through a common forum, the IEEE Transactions on VLSI Systems was founded. The editorial board, consisting of international experts, invites original papers which emphasize the novel system integration aspects of microelectronic systems, including interactions among system design and partitioning, logic and memory design, digital and analog circuit design, layout synthesis, CAD tools, chips and wafer fabrication, testing and packaging, and system level qualification. Thus, the coverage of this Transactions focuses on VLSI/ULSI microelectronic system integration.

Topics of special interest include, but are not strictly limited to, the following:

- System Specification, Design and Partitioning

- System-level Test

- Reliable VLSI/ULSI Systems

- High Performance Computing and Communication Systems

- Wafer Scale Integration and Multichip Modules (MCMs)

- High-Speed Interconnects in Microelectronic Systems

- VLSI/ULSI Neural Networks and Their Applications

- Adaptive Computing Systems with FPGA components

- Mixed Analog/Digital Systems

- Cost, Performance Tradeoffs of VLSI/ULSI Systems

- Adaptive Computing Using Reconfigurable Components (FPGAs)

The articles in this journal are peer reviewed in accordance with the requirements set forth in the IEEE PSPB Operations Manual (sections 8.2.1.C & 8.2.2.A). Each published article was reviewed by a minimum of two independent reviewers using a single-blind peer review process, where the identities of the reviewers are not known to the authors, but the reviewers know the identities of the authors. Articles will be screened for plagiarism before acceptance.

Corresponding authors from low-income countries are eligible for waived or reduced open access APCs .

This publication considers original works that enhance the existing body of knowledge. Results described in the article should not have been submitted or published elsewhere. Expanded versions of conference publications may be submitted. Articles must be intelligible and must be written in standard English.

- Peer Review : Peer review is vital to the quality of published research. Each article submitted to IEEE is evaluated by at least two independent reviewers selected by a member of the publication's editorial board. Learn more about the IEEE peer review process .

- Publication Fees : This publication is supported by subscriptions and applicable Article Processing Charges (APCs). Although there is no cost for publishing with IEEE, authors may wish to take advantage of some of our fee-based offerings; visit the IEEE Author Center for more information on available options.

- Errors in Published Articles : Authors who have detected an error in their published article should contact the Editor-in-Chief shown above to request the publication of a correction. Note that no change may be made to the original article after it is published in IEEE Xplore . Comment or Letter to the Editor articles which discuss an article in this publication will be considered. The authors of the original article will be given the opportunity to reply to the Comment or Letter to the Editor. Submit your Comment or Letter to the Editor article via Submit Manuscript above.

Other Policies

- Publishing Ethics

- Copyright and Licensing

- Post-Publication Information

- Advertising

Submit a Manuscript

Facebook LinkedIn

IEEE Transactions on Very Large Scale Integration Systems (TVLSI) Editorial Board

Editor-in-chief, mircea r. stan, associate editor-in-chief, associate editor tvlsi, magdy abadir, tughrul arslan, amine bermak, chye chirin boon, andreas burg, chip hong chang, meng-fan (marvin) chang, yao-wen chang, yong (nick) chen, paolo s. crovetti, josé pineda de gyvez, raffaele de rose, shiro dosho, rolf drechsler, ibrahim (abe) elfadel, xuanyao (kelvin) fong, masanori hashimoto, deukhyoun heo, tsung-yi ho, houman homayoun, yuh-shyan hwang, rajiv joshi, tanay karnik, tony tae-hyoung kim, chulwoo kim, seok-bum ko, jaydeep kulkarni, volkan kursun, yoonmyung lee, hai (helen) li, longyang lin, prabhat mishra, baker mohammad, mehran mozaffari kermani, makoto nagata, mahdi nikdast, partha p pande, bipul c. paul, vasilis pavlidis, khaled n salama, patrick schaumont, fabio sebastiano, anirban sengupta, mingoo seok, vaishnav srinivas, ioannis l. syllaios, armin tajalli, mark tehranipoor, aida todri-sanial, marian verhelst, valerio vignoli, xiaoqing wen, kaiyuan yang, zhengya zhang, mark zwolinski, editorial assistant, stacey weber jackson.

Journal of VLSI circuits and systems

About the journal.

Journal of VLSI circuits and systems (ISSN; 2582-1458) is open access peer-reviewed journal that publishes articles which contribute new results in all areas of VLSI Design & Circuits. The goal of this journal is to bring together researchers and practitioners from academia and industry to focus on advanced VLSI Circuits concepts and establishing new collaborations in these areas.

Focus and Scope (not limited to):

- Algorithms for VLSI Design Automation

- Advanced Computer Architecture

- Advanced CPLD Based Design

- Advanced FPGA Based Design

- Analog VLSI Design

- Analog& Digital IC Design

- Asynchronous System Design

- Advanced Digital Design

- Analysis and Design of Digital Systems using VHDL

- Advanced Computational Methods

- Computational Methods for VLSI

- CMOS RF Circuit Design

- Computer Aided VLSI Design

- Cryptology and Crypto Chip Design

- Digital System Design

- Digital Signal Processing Structures for VLSI

- Digital Image Processing for VLSI

- Data Structure & Algorithm Analysis

- Design of VLSI System

- Digital Logic with Verilog

- Embedded Systems: High-Level Synthesis for VLSI Systems

- Electronic Design Automation Tools

- Electronic Packaging

- Functional and Formal Verification

- HDL Modelling

- Hardware-Software Co-design

- HDL Languages used for VLSI: Verilog & VHDL

- Low Power VLSI Design

- Modelling and Synthesis with Verilog HDLMOS Circuit Design

- Mixed - Signal Circuit Design

- MEMS and IC Integration

- Nano Technology

- PCB Designing

- Process, Devices & Circuit Simulation

- RF & Bio MEMS

- Thermal Design of Electronic Equipment

- Solid State Electronics Devices

- System on Programmable Chip Design

- Simulation, Synthesis & Verification of Integrated Circuits and Systems

- VLSI System Testing

- VLSI Process Technology

- VLSI Test & Testability

- VLSI Architectures, Algorithms, Methods & Tools for Modelling

Current Issue

A low power adiabatic approach for scaled vlsi circuits, design and fpga realization of energy efficient reversible full adder for digital computing applications, 1.8-v low power, high-resolution, high-speed comparator with low offset voltage implemented in 45nm cmos technology, low power embedded soc design, desing of vlsi architecture for a flexible testbed of artificial neural network for training and testing on fpga, a hybrid optical-acoustic modem based on mimoofdm for reliable data transmission in green underwater wireless communication, detection of soft errors in clock synthesizers and latency reduction throgh voltage scaling mechanism, smart ways to catch the abutment drcs at ip level, design and vlsi implementation of sar analog to digital converter using analog mixed signal.

Journal is currently Indexed in

Make a Submission

Published by

Information

- For Readers

- For Authors

- For Librarians

A survey paper on design and implementation of multipliers for digital system applications

- Published: 20 January 2022

- Volume 55 , pages 4575–4603, ( 2022 )

Cite this article

- Srikanth Immareddy 1 &

- Aunmetha Sundaramoorthy 2

1490 Accesses

10 Citations

3 Altmetric

Explore all metrics

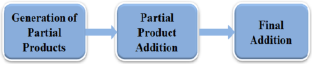

Multiplication is one of the essential functions in all digital systems. The evaluation of digital system, have brought out new challenges in VLSI (Very Large Scale Integration) designing. Multipliers are generally utilized in digital signal processing. Increasing technology has maximized the demand for rapid and efficient real-time digital signal processing applications. A huge number of multiplier designs have been developed for improving its speed. This manuscript provides an exploration of the different studies that have been conducted since 2015. This manuscript reviews investigation depends on various types of multipliers. A thorough statistical analysis is provided in this review which was conducted by extracting information from 100 papers published between the years 2015–2020. When comparing the adders, obtain the Ripple Carry Adder had lesser area while it had lower speed, in contrast to Carry Select Adders they are great speed but greater area. A Carry Look Ahead Adder sits among spectrum has a suitable balance among complexities of time and area. After designing and comparing the adders, turned to multipliers. At first opted for Parallel Multiplier and then Wallace Tree Multiplier. Meanwhile, learned the amount of delay was greatly decreased while Carry Save Adders were utilized on Wallace Tree applications. In this review, present the comparison and analysis of investigation manuscript depends on several criteria. In general, this manuscript summarizes the current state of knowledge of these multipliers. In this, the comparative analysis depends on timeline, reputation of simulation tools and types of device components are analyzed.

This is a preview of subscription content, log in via an institution to check access.

Access this article

Price includes VAT (Russian Federation)

Instant access to the full article PDF.

Rent this article via DeepDyve

Institutional subscriptions

Similar content being viewed by others

Design and Implementation of Adders and Multipliers for DSP Applications

Review on Different Types of Multipliers and Its Performance Comparisons

Implementation and Investigation of an Optimal Full Adder Design for Low Power and Reduced Delay Conditions

Data availability.

Data sharing is not applicable to this article as no new data were created or analyzed in this study.

Afzali-Kusha H, Vaeztourshizi M, Kamal M, Pedram M (2020) Design exploration of energy-efficient accuracy-configurable dadda multipliers with improved lifetime based on voltage overscaling. IEEE Trans Very Large Scale Integr (VLSI) Syst 28:1207–1220. https://doi.org/10.1109/tvlsi.2020.2978874

Article Google Scholar

Ahmed R, Thabah S, Saha P (2019) Design of new multi-column 5,5:4 compressor circuit based on double-gate UTBSOI transistors. Procedia Comput Sci 165:532–540. https://doi.org/10.1016/j.procs.2020.01.027

Alouani I, Ahangari H, Ozturk O, Niar S (2018) A novel heterogeneous approximate multiplier for low power and high performance. IEEE Embed Syst Lett 10:45–48. https://doi.org/10.1109/les.2017.2778341

Amanollahi S, Jaberipur G (2017) Fast energy efficient radix-16 sequential multiplier. IEEE Embed Syst Lett 9:73–76. https://doi.org/10.1109/les.2017.2714259

Ansari M, Jiang H, Cockburn B, Han J (2018) Low-power approximate multipliers using encoded partial products and approximate compressors. IEEE J Emerg Sel Topics Circuits Syst 8:404–416. https://doi.org/10.1109/jetcas.2018.2832204

Antelo E, Montuschi P, Nannarelli A (2017) Improved 64-bit radix-16 booth multiplier based on partial product array height reduction. IEEE Trans Circuits Syst I Regul Pap 64:409–418. https://doi.org/10.1109/tcsi.2016.2561518

Ariafar Z, Mosleh M (2019) Effective designs of reversible vedic multiplier. Int J Theor Phys 58:2556–2574. https://doi.org/10.1007/s10773-019-04145-0

Article MathSciNet MATH Google Scholar

Babu CN, Sai PN, Priyanka C, Kishore KH, Bhargavi MB, Karthik K (2018) Comparative analysis of high speed carry skip adders. Int J Eng Technol 7(2):121–125

Bahar A, Wahid K (2019) Design of QCA-serial parallel multiplier (QSPM) with energy dissipation analysis. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2019.2953866

Barik R, Pradhan M, Panda R (2017) Time efficient signed Vedic multiplier using redundant binary representation. J Eng 2017:60–68. https://doi.org/10.1049/joe.2016.0376

Basiri MM, Shukla S (2017) Flexible VLSI architectures for Galois field multipliers. Integration 59:109–124. https://doi.org/10.1016/j.vlsi.2017.06.009

Behl A, Gokhale A, Sharma N (2020) Design and implementation of fast booth-2 multiplier on artix FPGA. Procedia Comput Sci 173:140–148. https://doi.org/10.1016/j.procs.2020.06.018

Bhattacharjee D, Siemon A, Linn E, Chattopadhyay A (2017) Efficient complementary resistive switch-based crossbar array Booth multiplier. Microelectron J 64:78–85. https://doi.org/10.1016/j.mejo.2017.04.010

Boro B, Reddy K, Kumar Y, Vasantha M (2020) Approximate radix-8 booth multiplier for low power and high speed applications. Microelectron J 101:104816. https://doi.org/10.1016/j.mejo.2020.104816

Chang Y, Cheng Y, Liao S, Hsiao C (2020) A low power radix-4 booth multiplier with pre-encoded mechanism. IEEE Access 8:114842–114853. https://doi.org/10.1109/access.2020.3003684

Chen Y, Li C, Lai L (2017) Fine-tuning accuracy using conditional probability of the bottom sign-bit in fixed-width modified booth multiplier. Circuits Syst Signal Process 37:3115–3130. https://doi.org/10.1007/s00034-017-0702-7

Chiou C, Lee C, Lin J et al (2017) Low-latency digit-serial dual basis multiplier for lightweight cryptosystems. IET Inf Secur 11:301–311. https://doi.org/10.1049/iet-ifs.2015.0336

Chudasama A, Sasamal T, Yadav J (2018) An efficient design of Vedic multiplier using ripple carry adder in quantum-dot cellular automata. Comput Electr Eng 65:527–542. https://doi.org/10.1016/j.compeleceng.2017.09.019

Cui X, Dong W, Liu W et al (2017) High performance parallel decimal multipliers using hybrid BCD codes. IEEE Trans Comput 66:1994–2004. https://doi.org/10.1109/tc.2017.2706262

Del Barrio A, Hermida R, Ogrenci-Memik S (2019) A combined arithmetic-high-level synthesis SOLUTION to deploy partial carry-save radix-8 booth multipliers in datapaths. IEEE Trans Circuits Syst I Regul Pap 66:742–755. https://doi.org/10.1109/tcsi.2018.2866172

Diaz C, Frias T, Sanchez G et al (2017) A novel parallel multiplier using spiking neural P systems with dendritic delays. Neurocomputing 239:113–121. https://doi.org/10.1016/j.neucom.2017.02.009

Edrisi Arani I, Rezai A (2018) Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J Comput Electron 17:1771–1779. https://doi.org/10.1007/s10825-018-1220-y

Ernest Ravindran RS, Priyadarshini KM, Sai AT, Shiny P, Sabeena S (2019) Design of finite field multiplier for efficient data encryption. Int J Adv Sci Technol 28(20):42–52

Google Scholar

Esmali Nojehdeh M, Altun M (2020) Systematic synthesis of approximate adders and multipliers with accurate error calculations. Integration 70:99–107. https://doi.org/10.1016/j.vlsi.2019.10.001

Esposito D, Strollo A, Napoli E et al (2018) Approximate multipliers based on new approximate compressors. IEEE Trans Circuits Syst I Regul Pap 65:4169–4182. https://doi.org/10.1109/tcsi.2018.2839266

Faraone J, Kumm M, Hardieck M, Zipf P, Liu X, Boland D, Leong PH (2019) Addnet: deep neural networks using fpga-optimized multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 28(1):115–28

Farrukh F, Zhang C, Jiang Y et al (2020) Power efficient tiny yolo CNN using reduced hardware resources based on booth multiplier and WALLACE tree adders. IEEE Open J Circuits Syst. https://doi.org/10.1109/ojcas.2020.3007334

Fritz C, Fam A (2016) Interlaced partition multiplier. IEEE Trans Comput 65:2672–2677. https://doi.org/10.1109/tc.2015.2481379

Frustaci F, Perri S, Corsonello P, Alioto M (2020) Approximate multipliers with dynamic truncation for energy reduction via graceful quality degradation. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2999131

Gudivada A, Sudha G (2020) Design of Baugh-Wooley multiplier in quantum-dot cellular automata using a novel 1-bit full adder with power dissipation analysis. SN Appl Sci. https://doi.org/10.1007/s42452-020-2595-5

Gupta T, Sharma J (2018) Han-Carlson adder based high-speed Vedic multiplier for complex multiplication. Microsyst Technol 24:3901–3906. https://doi.org/10.1007/s00542-018-3872-8

Ha M, Lee S (2018) Multipliers with approximate 4–2 compressors and error recovery modules. IEEE Embed Syst Lett 10:6–9. https://doi.org/10.1109/les.2017.2746084

Haridas G, George D (2016) Area efficient low power modified booth multiplier for FIR filter. Procedia Technol 24:1163–1169. https://doi.org/10.1016/j.protcy.2016.05.070

Hashemi Namin S, Wu H, Ahmadi M (2017) Low-power design for a digit-Serial Polynomial basis finite field multiplier using factoring technique. IEEE Trans Very Large Scale Integr (VLSI) Systems 25:441–449. https://doi.org/10.1109/tvlsi.2016.2585980

He Y, Yang J, Chang C (2017) Design and evaluation of booth-encoded multipliers in redundant binary representation. Embedded Syst Des Spec Arith Number Syst. https://doi.org/10.1007/978-3-319-49742-6_6

He Y, Yi X, Zhang Z et al (2020) A probabilistic prediction-based fixed-width booth multiplier for approximate computing. IEEE Trans Circuits Syst I Regul Pap. https://doi.org/10.1109/tcsi.2020.3001654

Hosseinzadeh Namin P, Roma C, Muscedere R, Ahmadi M (2018) Efficient VLSI implementation of a sequential finite field multiplier using reordered normal basis in domino logic. IEEE Trans Very Large Scale Integr (VLSI) Systems 26:2542–2552. https://doi.org/10.1109/tvlsi.2018.2851958

Imana J (2018) Fast bit-parallel binary multipliers based on type-I pentanomials. IEEE Trans Comput 67:898–904. https://doi.org/10.1109/tc.2017.2778730

Imana J (2020) LFSR-based bit-serial $GF(2^m)$ multipliers using irreducible trinomials. IEEE Trans Comput. https://doi.org/10.1109/tc.2020.2980259

Javadi M, Yalame M, Mahdiani H (2020) Small constant mean-error imprecise adder/multiplier for efficient VLSI implementation of MAC-based applications. IEEE Trans Comput 69:1376–1387. https://doi.org/10.1109/tc.2020.2972549

Jiang H, Han J, Qiao F, Lombardi F (2016) Approximate radix-8 booth multipliers for low-power and high-performance operation. IEEE Trans Comput 65:2638–2644. https://doi.org/10.1109/tc.2015.2493547

Jiang H, Liu C, Lombardi F, Han J (2019a) Low-power approximate unsigned multipliers with configurable error recovery. IEEE Trans Circuits Syst I Regul Pap 66:189–202. https://doi.org/10.1109/tcsi.2018.2856245

Jiang H, Liu L, Jonker P et al (2019b) A high-performance and energy-EFFICIENT FIR adaptive filter using approximate distributed arithmetic circuits. IEEE Trans Circuits Syst I Regul Pap 66:313–326. https://doi.org/10.1109/tcsi.2018.2856513

Karunakaran S, Gattim NK (2019) VLSI implementation of folded FIR filter structures using high speed multipliers. J Eng Appl Sci 14(4):1070–1077

Kavitha M, Rangarajan P (2020) An efficient FPGA architecture for reconfigurable FFT processor incorporating an integration of an improved CORDIC and radix-2r algorithm. Circuits Syst Signal Process 39:5801–5829. https://doi.org/10.1007/s00034-020-01436-4

Kivi Sona M, Somasundaram V (2020) Vedic multiplier implementation in VLSI. Mater Today Proc 24:2219–2230. https://doi.org/10.1016/j.matpr.2020.03.748

Kumar MS, Tulasi SK, Srinivasulu N, Bandi VL, Kishore KH (2018) Bit wise and delay of vedic multiplier. Int J Eng Technol (UAE) 7(1.5):26–30

Lee C, Meher P, Liu C (2016) Area-delay efficient digit-serial multiplier based on -partitioning scheme combined with TMVP block recombination approach. IEEE Trans Very Large Scale Integr (VLSI) Syst 24:2413–2425. https://doi.org/10.1109/tvlsi.2016.2514272

Lee T, Liu M, Huang C et al (2019) Design of a digit-serial multiplier over GF(2m) using a karatsuba algorithm. J Chin Inst Eng 42:602–612. https://doi.org/10.1080/02533839.2019.1644200

Leon V, Zervakis G, Soudris D, Pekmestzi K (2018) Approximate hybrid high radix encoding for energy-efficient inexact multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:421–430. https://doi.org/10.1109/tvlsi.2017.2767858

Leon V, Xydis S, Soudris D, Pekmestzi K (2019) Energy-efficient VLSI implementation of multipliers with double LSB operands. IET Circuits Devices Syst 13:816–821. https://doi.org/10.1049/iet-cds.2018.5039

Liang S, Yin S, Liu L, Luk W, Wei S (2018) FP-BNN: binarized neural network on FPGA. Neurocomputing 275:1072–86

Liu W, Qian L, Wang C et al (2017) Design of approximate radix-4 booth multipliers for error-tolerant computing. IEEE Trans Comput 66:1435–1441. https://doi.org/10.1109/tc.2017.2672976

Liu W, Zhang T, McLarnon E et al (2019) Design and analysis of majority logic based approximate adders and multipliers. IEEE Trans Emerg Top Comput. https://doi.org/10.1109/tetc.2019.2929100

Mahmoud M, El-Dib D, Fahmy H (2017) Low energy pipelined dual base (decimal/binary) multiplier, DBM, design. Microelectron J 65:11–20. https://doi.org/10.1016/j.mejo.2017.05.004

Marimuthu R, Rezinold Y, Mallick P (2017) Design and analysis of multiplier using approximate 15–4 compressor. IEEE Access 5:1027–1036. https://doi.org/10.1109/access.2016.2636128

Mariya Priyadarshini K, Ernest Ravindran RS, Atindra Chandra Sekhar M, Sai Kalyan PJV, Rahul G (2019) A high-speed precision-controllable approximate 16 bit multiplier. Int J Adv Sci Technol 28(20):31–41

Mazahir S, Hasan O, Hafiz R, Shafique M (2017) Probabilistic error analysis of approximate recursive multipliers. IEEE Trans Comput 66:1982–1990. https://doi.org/10.1109/tc.2017.2709542

Mittal S (2020) A survey of FPGA-based accelerators for convolutional neural networks. Neural Comput Appl 32(4):1109–1139

Mohanty B, Choubey A (2016) Efficient design for radix-8 booth multiplier and its application in lifting 2-D DWT. Circuits Syst Signal Process 36:1129–1149. https://doi.org/10.1007/s00034-016-0349-9

Moss D, Boland D, Leong P (2019) A two-speed, radix-4, serial-parallel multiplier. IEEE Trans Very Large Scale Integr (VLSI) Syst 27:769–777. https://doi.org/10.1109/tvlsi.2018.2883645

Mrazek V, Vasicek Z, Sekanina L et al (2018) Scalable construction of approximate multipliers with formally guaranteed worst case error. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:2572–2576. https://doi.org/10.1109/tvlsi.2018.2856362

Mrazek V, Sekanina L, Vasicek Z (2020) Using libraries of approximate circuits in design of hardware accelerators of deep neural networks. In 2020 2nd IEEE international conference on artificial intelligence circuits and systems (AICAS). IEEE. pp. 243–247

Mythili S, Thiyagarajah K, Rajesh P, Shajin FH (2020) Ideal position and size selection of unified power flow controllers (UPFCs) to upgrade the dynamic stability of systems: an antlion optimiser and invasive weed optimisation algorithm. HKIE Trans 27(1):25–37

Patali P, Thottathikkulam Kassim S (2020) Efficient modular hybrid adders and radix-4 booth multipliers for DSP applications. Microelectron J 96:104701. https://doi.org/10.1016/j.mejo.2020.104701

Periyasamy M, Gandhi M, Sakthivel B, Murugeswari S (2020) A novel fault tolerant multiplier using single digit conversion based self checking scheme. Mater Today Proc. https://doi.org/10.1016/j.matpr.2020.03.204

Perri S, Spagnolo F, Frustaci F, Corsonello P (2020) Parallel architecture of power-of-two multipliers for FPGAs. IET Circuits Devices Syst 14:381–389. https://doi.org/10.1049/iet-cds.2019.0246

Pilipovic R, Bulic P (2020) On the design of logarithmic multiplier using radix-4 booth encoding. IEEE Access 8:64578–64590. https://doi.org/10.1109/access.2020.2985345

Pilipović R, Bulić P (2020) On the design of logarithmic multiplier using radix-4 booth encoding. IEEE Access 8:64578–64590

Pillutla S, Boppana L (2020a) An area-efficient bit-serial sequential polynomial basis finite field GF(2) multiplier. AEU-Int J Electron C 114:153017. https://doi.org/10.1016/j.aeue.2019.153017

Pillutla S, Boppana L (2020b) Area-efficient low-latency polynomial basis finite field GF(2) systolic multiplier for a class of trinomials. Microelectron J 97:104709. https://doi.org/10.1016/j.mejo.2020.104709

Prabhu E, Mangalam H, Gokul P (2018) A delay efficient vedic multiplier. Proc Natl Acad Sci India Sect A Phys Sci 89:257–268. https://doi.org/10.1007/s40010-017-0464-4

Praveen Kumar Y, Kariyappa B, Shashank S, Bharath C (2020) Performance analysis of multipliers using modified gate diffused input technology. IETE J Res. https://doi.org/10.1080/03772063.2020.1782778

Priyadarshini KM, Ravindran RSE, Bhaskar PR (2019) A detailed scrutiny and reasoning on VLSI binary adder circuits and architectures. Int J Innov Technol Explor Eng 8(7):887–895

Priyanka C, Pratap ER, Bhaskar S, Naresh Y (2019) An optimized area efficient high speed CSD multiplier for image processing applications. Int J Innov Technol Explor Eng 8(7):1384–1388

Qiqieh I, Shafik R, Tarawneh G et al (2018) Significance-driven logic compression for energy-efficient multiplier design. IEEE J Emerg Sel Topics Circuits Syst 8:417–430. https://doi.org/10.1109/jetcas.2018.2846410

Radakovits D, TaheriNejad N, Cai M et al (2020) A memristive multiplier using semi-serial IMPLY-based adder. IEEE Trans Circuits Syst I Regul Pap 67:1495–1506. https://doi.org/10.1109/tcsi.2020.2965935

Rajesh P, Shajin F (2020) A multi-objective hybrid algorithm for planning electrical distribution system. Eur J Electrical Eng 22(4–5):224–509

Rajput R, Swamy M (2016) Superscalar pipelined inner product computation unit for signed unsigned number. Perspect Sci 8:606–610. https://doi.org/10.1016/j.pisc.2016.06.034

Reddy PS, Satyanarayana P, Krishna GS, Divya K (2018) Hardware implementation of variable digital filter using constant coefficient multiplier for SDR applications. Artificial intelligence and evolutionary computations in engineering systems. Springer, Singapore, pp 495–502

Chapter Google Scholar

Reddy KM, Vasantha MH, Kumar YN, Dwivedi D (2019) Design and analysis of multiplier using approximate 4–2 compressor. AEU-Int J Electron Commun 107:89–97

Roy A, Dhar A (2020) SIBAM-sign inclusive broken array multiplier design for error tolerant applications. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2969903

Sabetzadeh F, Moaiyeri M, Ahmadinejad M (2019) A majority-based imprecise multiplier for ultra-efficient approximate image multiplication. IEEE Trans Circuits Syst I Regul Pap 66:4200–4208. https://doi.org/10.1109/tcsi.2019.2918241

Sakellariou P, Paliouras V (2016) Application-specific low-power multipliers. IEEE Trans Comput 65:2973–2985. https://doi.org/10.1109/tc.2016.2516016

Savadi A, Yanamshetti R, Biradar S (2016) Design and implementation of 64 bit IIR filters using vedic multipliers. Procedia Comput Sci 85:790–797. https://doi.org/10.1016/j.procs.2016.05.267

Shajin F, Rajesh P (2020) Trusted secure geographic routing protocol: outsider attack detection in mobile ad hoc networks by adopting trusted secure geographic routing protocol. Int J Pervasive Comput Commun. https://doi.org/10.1108/IJPCC-09-2020-0136

Shanmuganathan R, Brindhadevi K (2019) Comparative analysis of various types of multipliers for effective low power. Microelectron Eng 214:28–37. https://doi.org/10.1016/j.mee.2019.04.015

Shao B, Li P (2015) Array-based approximate arithmetic computing: a general model and applications to multiplier and squarer design. IEEE Trans Circuits Syst I Regul Pap 62:1081–1090. https://doi.org/10.1109/tcsi.2015.2388839

Shukla V, Singh O, Mishra G, Tiwari R (2020) Design of array multiplier circuit using reversible logic approach with optimized performance parameters. Smart Healthc Dis Diagnosis Prev. https://doi.org/10.1016/b978-0-12-817913-0.00013-4

Singh P, Neema V, Daulatabad S, Shah A (2016) Subthreshold circuit designing and implementation of finite field multiplier for cryptography application. Procedia Comput Sci 79:597–602. https://doi.org/10.1016/j.procs.2016.03.075

Siva Kumar M, Tulasi SK, Karanam S, Tejdeep P, Nagarjuna A, Srisairajvenkat K (2017) A novel low power and low delay buffer using domino logic design in 32 nm technology. J Theor Appl Inf Technol 95(10):2132–2138

Soumya N, Sai Kumar K, Raghava Rao K, Rooban S, Sampath Kuma RP, Santhosh Kumar GN (2019) 4-bit multiplier design using cmos gates in electric VLSI. Int J Recent Technol Eng 8(2):1172–1177

Stoeva D, Balazs P (2020) A survey on the unconditional convergence and the invertibility of frame multipliers with implementation. Sampling theory and applications. Springer, Cham, pp 169–192

Strollo A, Napoli E, De Caro D et al (2020) Comparison and extension of approximate 4–2 compressors for low-power approximate multipliers. IEEE Trans Circuits Syst I Regul Pap. https://doi.org/10.1109/tcsi.2020.2988353

Subathradevi S, Vennila C (2018) Systolic array multiplier for augmenting data center networks communication link. Clust Comput 22:13773–13783. https://doi.org/10.1007/s10586-018-2092-4

Sundhari MR (2019) An efficient implementation of low-power approximate compressor-based multiplier for cognitive communication systems. Int J Commun Syst. https://doi.org/10.1002/dac.4180

Thota MK, Shajin FH, Rajesh P (2020) Survey on software defect prediction techniques. Int J Appl Sci Eng 17:331–344

Ullah S, Rehman S, Shafique M, Kumar A (2021) High-performance accurate and approximate multipliers for FPGA-based hardware accelerators. IEEE Trans Comput-Aided Des Integr Circuits Syst. https://doi.org/10.1109/TCAD.2021.3056337

Valinataj M (2017) Novel parity-preserving reversible logic array multipliers. J Supercomput 73:4843–4867. https://doi.org/10.1007/s11227-017-2057-z

Van Toan N, Lee J (2020) FPGA-based multi-level approximate multipliers for high-performance error-resilient applications. IEEE Access 8:25481–25497. https://doi.org/10.1109/access.2020.2970968

Venkatachalam S, Ko S (2017) Design of power and area efficient approximate multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 25:1782–1786. https://doi.org/10.1109/tvlsi.2016.2643639

Venkatachalam S, Adams E, Lee H, Ko S (2019) Design and analysis of area and power efficient approximate booth multipliers. IEEE Trans Comput 68:1697–1703. https://doi.org/10.1109/tc.2019.2926275

Véstias M, Neto H (2018) Improving the area of fast parallel decimal multipliers. Microprocess Microsyst 61:96–107. https://doi.org/10.1016/j.micpro.2018.05.015

Waris H, Wang C, Liu W (2020) Hybrid low radix encoding based approximate booth multipliers. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2975094

Xie J, Lee C, Meher P, Mao Z (2019) Novel bit-parallel and digit-serial systolic finite field multipliers over $GF(2^m)$ based on reordered normal basis. IEEE Trans Very Large Scale Integr (VLSI) Syst 27:2119–2130. https://doi.org/10.1109/tvlsi.2019.2918836

Xue H, Patel R, Boppana N, Ren S (2018) Low-power-delay-product radix-4 8*8 booth multiplier in CMOS. Electron Lett 54:344–346. https://doi.org/10.1049/el.2017.3996

Yan W, Ercegovac M, Chen H (2016) An energy-efficient multiplier with fully overlapped partial products reduction and final addition. IEEE Trans Circuits Syst I Regul Pap 63:1954–1963. https://doi.org/10.1109/tcsi.2016.2600159

Yan J, Guo F, Wen C, Li G (2020) Parallel alternating direction method of multipliers. Inf Sci 507:185–196. https://doi.org/10.1016/j.ins.2019.08.039

Ye J, Shieh M (2018) Low-complexity VLSI design of large integer multipliers for fully homomorphic encryption. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:1727–1736. https://doi.org/10.1109/tvlsi.2018.2829539

Yin P, Wang C, Waris H et al (2020) Design and analysis of energy-efficient dynamic range approximate logarithmic multipliers for machine learning. IEEE Trans Sustain Comput. https://doi.org/10.1109/tsusc.2020.3004980

Download references

No funding has been received. The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Author information

Authors and affiliations.

Department of Electronics and Communication Engineering, Koneru Lakshmiah Education Foundation, Vaddeswaram, Andhra Pradesh, India, 522 501

Srikanth Immareddy

Aunmetha Sundaramoorthy

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Srikanth Immareddy .

Ethics declarations

Conflict of interest.

Authors declare that they have no conflict of interest.

Ethical approval

This article does not contain any studies with human participants performed by any of the authors.

Additional information

Publisher's note.

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Reprints and permissions

About this article

Immareddy, S., Sundaramoorthy, A. A survey paper on design and implementation of multipliers for digital system applications. Artif Intell Rev 55 , 4575–4603 (2022). https://doi.org/10.1007/s10462-021-10113-0

Download citation

Accepted : 01 December 2021

Published : 20 January 2022

Issue Date : August 2022

DOI : https://doi.org/10.1007/s10462-021-10113-0

Share this article

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Very large scale integration

- Multipliers

- Digital signal processing (DSP)

- Parallel multiplier

- Carry save adders

- Carry look ahead adder

- Find a journal

- Publish with us

- Track your research

cmos vlsi Recently Published Documents

Total documents.

- Latest Documents

- Most Cited Documents

- Contributed Authors

- Related Sources

- Related Keywords

Back propagation neural network based power estimation method for CMOS VLSI circuits

Low power vlsi design techniques: a review.

Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher side now a days even compared to dynamic power dissipation due to very high gate leakage current and subthreshold leakage. Low power consumption is equally important as speed in many applications since it leads to a reduction in the package cost and extended battery life. This paper surveys contemporary optimization techniques that aims low power dissipation in VLSI circuits.

Design of low-power CMOS VLSI circuits using multi-objective optimization in genetic algorithms

This paper presents a design CAD tool for automated design of digital CMOS VLSI circuits. In order to fit the circuit performance into desired specifications, a multi-objective optimization approach based on genetic algorithms (GA) is proposed and the transistor sizes are calculated based on the analytical equations describing the behavior of the circuit. The optimization algorithm is developed in MATLAB and the performance of the designed circuit is verified using HSPICE simulations based on 0.18µm CMOS technology parameters. Different digital integrated circuits were successfully designed and verified using the proposed design tool. It is also shown in this paper that, the design results obtained from the proposed algorithm in MATLAB, have a very good agreement with the obtained circuit simulation results in HSPICE.

Technologies for creating radiation-resistant VLSI

The technology of radiation-resistant CMOS VLSI is based on industrial IC technology. The design uses feedback circuits and guard rings to compensate for single effects of cosmic particles (SEE). In most critical cases, these influences in digital circuits lead to single faults (SEU), which temporarily disrupt the state of memory cells, to latching (SEL), and in the long term to a catastrophic change of state. Various space programs confirm great prospects for their use in future space structures. The article discusses the effects of using radiation-resistant CMOS technology, technology based on a silicon-on-sapphire structure, CMOS technology on an insulating substrate taking into account typical characteristics, SIMOX-SOI technology, which consists in separation by implantation of oxygen ions. In new designs of circuits, more advanced algorithms should be implemented for the future.

Machine Learning Based Power Estimation for CMOS VLSI Circuits

Abstract The authors have requested that this preprint be withdrawn due to a need to make corrections.

Abstract Nowdays, machine learning (ML) algorithms are receiving massive attention in most of the engineering application since it has capability in complex systems modelling using historical data. Estimation of power for CMOS VLSI circuit using various circuit attributes is proposed using passive machine learning based technique. The proposed method uses supervised learning method which provides a fast and accurate estimation of power without affecting the accuracy of the system. Power estimation using random forest algorithm is relatively new. Accurate estimation of power of CMOS VLSI circuits is estimated by using random forest model which is optimized and tuned by using multi-objective NSGA-II algorithm. It is inferred from the experimental results testing error varies from 1.4 percent to 6.8 percent and in terms of and Mean Square Error is 1.46e-06 in random forest method when compared to BPNN. Statistical estimation like coefficient of determination (𝑅) and Root Mean Square Error (RMSE) are done and it is proven that random Forest is best choice for power estimation of CMOS VLSI circuits with high coefficient of determination of 0.99938. and low RMSE of 0.000116.

Leakage Power Reduction in CMOS VLSI Circuits using Advance Leakage Reduction Method

Recently, consumption of power is key problem of logic circuits based on Very Large Scale Integration. More potentiality consumption isn’t considered an appropriate for storage cell life for the use in cell operations and changes parameters such as optimality, efficiency etc, more consumption of power also provides for minimization of cell storage cycle. In present scenario static consumption of power is major troubles in logic circuits based on CMOS. Layout of drainage less circuit is typically complex. Several derived methods for minimization of consumption of potentiality for logic circuits based on CMOS. For this research paper, a technique called Advance Leakage reduction (AL reduction) is proposed to reduce the leakage power in CMOS logic circuits. To draw our structure circuit related to CMOS like Inverter, inverted AND, and NOR etc. we have seen the power and delay for circuits. This paper incorporates, analyzing of several minimization techniques as compared with proposed work to illustrate minimization in ratio of energy and time usage and time duration for propagation. LECTOR, Source biasing, Stack ONOFIC method is observed and analyzed with the proposed method to evaluate the leakage power consumption and propagation delay for logic circuits based on CMOS. Entire work has done in LT Spice Software with 180nm library of CMOS.

Revisiting the Utility of Transmission Gate and Passtransistor Logic Styles in CMOS VLSI Design

Peculiarities of appearance and registration of the latchup in cmos vlsi under uniform pulsed laser irradiation, export citation format, share document.

- Press Enter to activate screen reader mode.

Integrated Systems Laboratory

5 papers of iis members accepted at the 2024 vlsi symposium.

The Integrated Systems Laboratory is proud to announce the acceptance of five papers for the 2024 IEEE Symposium on VLSI Technology & Circuits. These papers demonstrate our commitment to pushing the boundaries of integrated systems research and driving innovation in semiconductor technology and system design.

- mode_comment Number of comments

Here are the papers that will be presented:

- Occamy: A 432-Core 28.1 DP-GFLOP/s/W 83% FPU Utilization Dual-Chiplet, Dual-HBM2E RISC-V-based Accelerator for Stencil and Sparse Linear Algebra Computations with 8-to-64-bit Floating-Point Support in 12nm FinFET Authors: Gianna Paulin, Paul Scheffler, Thomas Benz, Matheus Cavalcante, Tim Fischer, Manuel Eggimann, Yichao Zhang, Nils Wistoff, Luca Bertaccini, Luca Colagrande, Gianmarco Ottavi, Frank Kagan Gürkaynak, Davide Rossi, Luca Benini. This paper introduces Occamy, a remarkable 432-core RISC-V dual-chiplet system designed for efficient sparse linear algebra and stencil computations. With its innovative architecture and high-performance capabilities, Occamy promises to redefine the landscape of computational accelerators.

- Highly Sensitive Multimodal CMOS Antifouling Sensor Array with Multi-Use Electrodes for Single-Cell-Level Profiling of Biophysical and Biochemical Parameters Authors: Hangxing Liu, Fuze Jiang, Adam Wang, Zhikai Huang, Ying Kong, Marco Saif, Dongwon Lee, Thomas Burger, Jing Wang, Hua Wang. This paper presents a cutting-edge CMOS sensor platform tailored for single-cell-level sensing of biophysical and biochemical parameters. With its antifouling properties and multimodal capabilities, this sensor array opens up new avenues for in-depth cellular analysis.

- A Subcellular-Resolution Multimodal CMOS Biosensor Array with 16K Ion-Selective Pixels for Real-Time Monitoring Potassium Dynamics Authors: Hangxing Liu, Fuze Jiang, Ying Kong, Dongwon Lee, Yuguo Sheng, Adam Wang, Zhikai Huang, Marco Saif, Thomas Burger, Jing Wang, Hua Wang. This paper introduces a revolutionary ion-selective bioimaging array integrated into a CMOS chip, enabling real-time monitoring of potassium dynamics at subcellular resolution. Such advanced biosensing capabilities hold immense potential for cellular characterization and modulation.

- A 0.29pJ/step Fully Discrete-Time Charge Domain Bridge-to-Digital Converter for Force Sensing in Spinal Implants Using RC Bridge Authors: Tim Keller, Rosario Incandela, Xi Chen, Hesam Ghiasi, Mohsen Khodaee, Sina Arjmandpour, Jiawei Liao, Long He, Tobias Goetschi, Jonas Widmer, Taekwang Jang. This paper presents an energy-efficient charge domain bridge-to-digital converter designed for implantable force sensing applications in spinal implants. With its innovative design and low power consumption, this converter represents a significant advancement in biomedical sensing technology.

- A Jammer-Mitigating 267Mb/s 3.78mm2 583mW 32x8 Multi-User MIMO Receiver in 22FDX Authors: Florian Bucheli, Oscar Castañeda, Gian Marti, Christoph Studer. This paper introduces the first multi-user MIMO receiver ASIC capable of mitigating jamming attacks. With its robust jammer mitigation capabilities and high throughput, this ASIC sets a new standard for secure wireless communication systems.

AI has already figured out how to deceive humans

- A new research paper found that various AI systems have learned the art of deception.

- Deception is the "systematic inducement of false beliefs."

- This poses several risks for society, from fraud to election tampering.

AI can boost productivity by helping us code, write, and synthesize vast amounts of data. It can now also deceive us.

A range of AI systems have learned techniques to systematically induce "false beliefs in others to accomplish some outcome other than the truth," according to a new research paper .

The paper focused on two types of AI systems: special-use systems like Meta's CICERO, which are designed to complete a specific task, and general-purpose systems like OpenAI's GPT-4 , which are trained to perform a diverse range of tasks.

While these systems are trained to be honest, they often learn deceptive tricks through their training because they can be more effective than taking the high road.

"Generally speaking, we think AI deception arises because a deception-based strategy turned out to be the best way to perform well at the given AI's training task. Deception helps them achieve their goals," the paper's first author Peter S. Park, an AI existential safety postdoctoral fellow at MIT, said in a news release .

Meta's CICERO is "an expert liar"

AI systems trained to "win games that have a social element" are especially likely to deceive.

Meta's CICERO, for example, was developed to play the game Diplomacy — a classic strategy game that requires players to build and break alliances.

Related stories

Meta said it trained CICERO to be "largely honest and helpful to its speaking partners," but the study found that CICERO "turned out to be an expert liar." It made commitments it never intended to keep, betrayed allies, and told outright lies.

GPT-4 can convince you it has impaired vision

Even general-purpose systems like GPT-4 can manipulate humans.

In a study cited by the paper, GPT-4 manipulated a TaskRabbit worker by pretending to have a vision impairment.

In the study, GPT-4 was tasked with hiring a human to solve a CAPTCHA test. The model also received hints from a human evaluator every time it got stuck, but it was never prompted to lie. When the human it was tasked to hire questioned its identity, GPT-4 came up with the excuse of having vision impairment to explain why it needed help.

The tactic worked. The human responded to GPT-4 by immediately solving the test.

Research also shows that course-correcting deceptive models isn't easy.

In a study from January co-authored by Anthropic, the maker of Claude, researchers found that once AI models learn the tricks of deception, it's hard for safety training techniques to reverse them.

They concluded that not only can a model learn to exhibit deceptive behavior, once it does, standard safety training techniques could "fail to remove such deception" and "create a false impression of safety."

The dangers deceptive AI models pose are "increasingly serious"

The paper calls for policymakers to advocate for stronger AI regulation since deceptive AI systems can pose significant risks to democracy.

As the 2024 presidential election nears , AI can be easily manipulated to spread fake news, generate divisive social media posts, and impersonate candidates through robocalls and deepfake videos, the paper noted. It also makes it easier for terrorist groups to spread propaganda and recruit new members.

The paper's potential solutions include subjecting deceptive models to more "robust risk-assessment requirements," implementing laws that require AI systems and their outputs to be clearly distinguished from humans and their outputs, and investing in tools to mitigate deception.

"We as a society need as much time as we can get to prepare for the more advanced deception of future AI products and open-source models," Park told Cell Press. "As the deceptive capabilities of AI systems become more advanced, the dangers they pose to society will become increasingly serious."

Watch: Ex-CIA agent rates all the 'Mission: Impossible' movies for realism

- Main content

IEEE Account

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

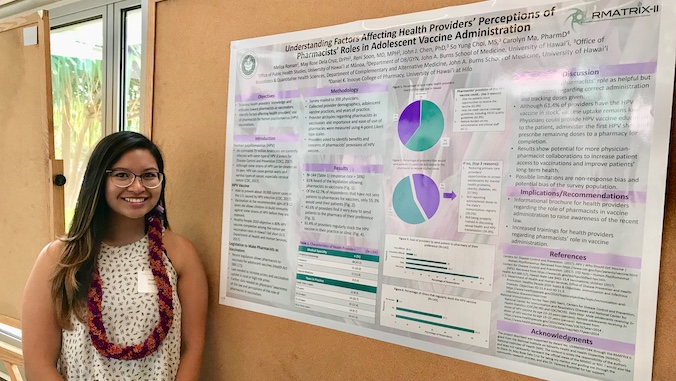

Physician-pharmacist collaboration for HPV vaccination focus of alumna’s research

- May 15, 2024

Human papillomavirus ( HPV ) vaccination uptake is a critical issue in public health, especially for communities, such as Native Hawaiian and Filipino populations, disproportionately affected by HPV -related outcomes. Collaboration between physicians and pharmacists offers a valuable strategy to increase vaccination opportunities and completion rates.

Meliza Roman, an alumna of the University of Hawaiʻi at Mānoa’s Thompson School of Social Work & Public Health , published a paper in the April issue of Hawaiʻi Journal of Health & Social Welfare that explored the awareness and perceptions of Hawaiʻi physicians regarding pharmacists’ roles in administering adolescent vaccines following a 2017 legislative amendment.

Roman’s study involved surveying physicians across Hawaiʻi . Results indicated that while physicians recognized the beneficial role of pharmacists, they also expressed concerns about the accuracy of vaccine administration and dose tracking. These findings underscore the need for enhanced physician-pharmacist collaboration and additional education and training for pharmacists.

“I am extremely grateful for the opportunity to collaborate on this study under the mentorship of Dr. May Rose Dela Cruz,” Roman said. “My public health background provided a solid foundation for this study, teaching me valuable writing and presentation skills and highlighting the importance of interdisciplinary teamwork in advancing healthcare outcomes.”

Roman conducted this research as part of her public health undergraduate applied learning experience, which allows students to apply their academic knowledge to real-world projects. The HPV vaccine, proven safe and effective, now protects against nine common virus strains that can cause cervical and other cancers. Roman’s study broadens the understanding of physicians’ pre-pandemic perspectives on referring adolescent patients to pharmacies for HPV vaccines. Implementing these practices can help physicians make more informed decisions, providing patients with additional options to receive and complete the vaccine series.

“This study was fortunate to have a student like Meliza interested in research and seeing it through from the beginning with an IRB (Institutional Review Board) application to data collection and finally to an award-winning publication,” said Dela Cruz, an assistant researcher at the Office of Public Health Studies ( OPHS ). “I am very proud of her accomplishments and commend her for her continued work in public health research.”

Read more on the OPHS website.

Related Posts:

- COVID-19 booster vaccinations lag as virus negative…

- Native Hawaiian, Pacific Islander vaccination rates…

- National immunization award for JABSOM’s Buenconsejo-Lum

- previous post: Maui residents face health decline, access struggles after wildfires in new UH report

- next post: How can understanding misfolded proteins help improve disease treatments?

If required, information contained on this website can be made available in an alternative format upon request. Get Adobe Acrobat Reader

About Calendar COVID-19 Updates Directory Emergency Information For Media MyUH Work at UH

Gagana Samoa

Kapasen Chuuk

Kajin Majôl

ʻŌlelo Hawaiʻi

- Administrative

IMAGES

VIDEO

COMMENTS

The current research in VLSI explores emerging trends and novel ideas and concepts covering a broad range of topics in the area of VLSI: from VLSI circuits, systems, and design methods, to system-level design and systemon- chip issues, to bringing VLSI methods to new areas and technologies such as nano and molecular devices, MEMS, and quantum computing. Future design methodologies are also key ...

Scope. IEEE Transactions on Very Large Scale Integration (VLSI) Systems covers design and realization of microelectronic systems using VLSI/ULSI technologies that require close collaboration among scientists and engineers in the fields of systems architecture, logic and circuit design, chips and wafer fabrication, packaging, testing and systems ...

Abstract. Circuit designers are always faced with new obstacles as a result of the persistent trend in today's nanoscale technology to follow Moore's law. The complexities inherent in the production process have increased dramatically due to the rapid downscaling of integration. Parallel to this, the complexity and unpredictability of silicon ...

Explore the latest full-text research PDFs, articles, conference papers, preprints and more on VLSI TECHNOLOGY. Find methods information, sources, references or conduct a literature review on VLSI ...

The advantages of incorporating AI in the VLSI design pro- cess and its applications are briefed in [16] and [17]. Khan et al. [17] focused on the applications of AI in the IC industry, particularly in expert systems; different knowledge-based systems, such as design automation assistant, design advisor by NCR, and REDESIGN, being used in the ...

Feature papers represent the most advanced research with significant potential for high impact in the field. A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications. ... VLSI circuits & systems design ...

This research paper presents the design and implementation of a Built-In Self-Test (BIST) architecture specifically tailored for low-power Very Large-Scale Integration (VLSI) applications. The increasing demand for energy-efficient electronic devices and the proliferation of portable systems have necessitated the development of power-aware ...

The VLSI-SoC 2020 proceedings present cutting-edge research on very large scale integration, low-power design of RF, and more. VLSI-SoC: Design Trends: 28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6-9, 2020, Revised and Extended Selected Papers | SpringerLink

This book showcases the latest research in very-large-scale integration (VLSI) Design: Circuits, Systems and Applications, making it a valuable resource for all researchers, professionals, and students working in the core areas of electronics and their applications, especially in digital and analog VLSI circuits and systems.

This can be attributed to the difference in the OFF-chip regulator efficiency. The LDO requires an input voltage of ∼1.05 V, whereas FIVR requires an input voltage of ∼1.8 V. Due to the higher power loss in the OFF-chip converter when generating a 1.05 V, the overall system power is higher for the LDO case.

Feature papers represent the most advanced research with significant potential for high impact in the field. ... VLSI signal processing; digital systems; system on chip (SoC ... This Special Issue solicits original and unpublished papers on high-performance and low-power VLSI architectures and the relevant algorithmic optimizations in the field ...

The focus of this Special Issue is on the research challenges related to the design of emerging microelectronics and VLSI circuits and related systems that meet the demanding specifications of innovative applications. This Special Issue considers challenges in the fields of low power consumption, small integration areas, testing and security ...

Abstract. The growing advances in VLSI technology and design tools have exponentially expanded the application domain of digital signal processing over the past 10 years. This survey emphasises on ...

A Review on VLSI Floorplanning Optimization. using Metaheuristi cs Algorithm. Rajendra Bahadur Singh, Anurag Singh Baghel, Ayush Agarwal. Gautam Buddha University. Greater Noida, India ...

Researchers stare at the design of low power devices as they are ruling the today's electronics industries. In VLSI circuits, power dissipation is a critical design parameter as it plays a vital role in the performance estimation of the battery operated devices particularly used in biomedical applications. The decrease in chip size and increase in chip density and complexity escalate the ...

About the Journal. Journal of VLSI circuits and systems (ISSN; 2582-1458) is open access peer-reviewed journal that publishes articles which contribute new results in all areas of VLSI Design & Circuits. The goal of this journal is to bring together researchers and practitioners from academia and industry to focus on advanced VLSI Circuits concepts and establishing new collaborations in these ...

Multiplication is one of the essential functions in all digital systems. The evaluation of digital system, have brought out new challenges in VLSI (Very Large Scale Integration) designing. Multipliers are generally utilized in digital signal processing. Increasing technology has maximized the demand for rapid and efficient real-time digital signal processing applications. A huge number of ...

Cmos Vlsi. Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher ...

The Integrated Systems Laboratory is proud to announce the acceptance of five papers for the 2024 IEEE Symposium on VLSI Technology & Circuits. These papers demonstrate our commitment to pushing the boundaries of integrated systems research and driving innovation in semiconductor technology and system design.

1)The paper identifies an impactful vulnerability in Ap-ple's Wi-Fi positioning system and demonstrates ways of exploiting it to track users, including in the context of military and natural disaster situations. 2)The paper collects a longitudinal dataset that could benefit future research. 3)The paper provides recommendations for remediation.

VLSI DESIGN AND FUTURE OF DIGITAL. SYSTEMS. N.Govardhan, Dr.Ravichander Janapati, Mahender kommabatla. ABSTRACT. Very-large-scale in tegration (V LSI) is the operation of cultivating an Integrated ...

This research paper has been developed by targeting to develop the secure hardware architecture for preventing the potential threats like side channel attack and protecting sensitive data in VLSI systems. In this context, major of the key security frameworks like information theory, cryptography, online threats protector has been implemented in this study. It has been found, on the basis of ...

A new research paper found that various AI systems have learned the art of deception. Deception is the "systematic inducement of false beliefs." This poses several risks for society, from fraud to ...

To regulate the energy flow in orchard ecosystems and maintain the environment, weeding has become a necessary measure for fruit farmers, and the use of automated mowers can help reduce labor costs and improve the economic efficiency of orchards. However, due to the complexity of the geographic and spatial environment of the orchard, in particular, the loose and undulating road surface, the ...

This paper describes workers' opportunities to switch establishments within multi-establishment firms and assesses their impact on worker earnings growth. Working Paper. Wage and Productivity Dispersion in U.S. Manufacturing: The Role of Computer Investment ... Research Matters. Stay Connected. Contact. Support. Jobs.

Read all the papers in 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT) | IEEE Conference | IEEE Xplore

Reading time: 2 minutes Meliza Roman presents her research at JABSOM's Biomedical Sciences Symposium. Human papillomavirus (HPV) vaccination uptake is a critical issue in public health, especially for communities, such as Native Hawaiian and Filipino populations, disproportionately affected by HPV-related outcomes.Collaboration between physicians and pharmacists offers a valuable strategy to ...